文 | 半导体产业纵横,作者 | 俊熹

9月3日,一则消息在科技圈引起了轩然大波:谷歌开始对外出售TPU了。

据报道,谷歌近期已在接触那些主要租赁英伟达芯片的小型云服务提供商,敦促他们在其数据中心也托管谷歌自家的AI处理器,也就是TPU。

谷歌已与至少一家云服务提供商——总部位于伦敦的Fluidstack——达成协议,将在纽约的一个数据中心部署其TPU。

谷歌的努力不止于此。据报道,该公司还向其他以英伟达为核心的服务商寻求类似的合作,其中包括正在为OpenAI建造数据中心的Crusoe,以及向微软租赁芯片并与OpenAI签有供应合同的英伟达“亲儿子”CoreWeave。

9月9日,花旗分析师因TPU竞争加剧将英伟达目标价下调至200美元,预计2026年GPU销售额将因此减少约120亿美元。

明眼人都能看出来的是,谷歌和英伟达之间的大战,已经开始了。而它们争夺的,将是AI计算这个真正的万亿美元市场。

然而,谷歌对这一战的准备,其实比我们想象的都要久。

TPU,AI计算的最优解?

早在2006年,谷歌的内部就讨论过在自家的数据中心中部署GPU、FPGA或ASIC的可能性。不过,当时只有少数应用程序能够在这些特殊硬件上运行,而谷歌大型数据中心的过剩算力也完全够它们使用了。因此,部署特殊硬件的计划被搁置。

然而,到了2013年,谷歌的研究人员发现:如果人们每天使用语音搜索并通过深度神经网络进行3分钟的语音识别,那么当时谷歌的数据中心需要双倍的算力才能满足日益增长的计算需求。

而如果仅通过扩大数据中心规模来满足算力需求,不但耗时,而且成本高昂。于是,在这个背景下,谷歌开始了TPU的设计。

谷歌的TPU是为AI计算而生的ASIC芯片,它专注于实现两个核心目标:极高的矩阵乘法吞吐量与卓越的能效。

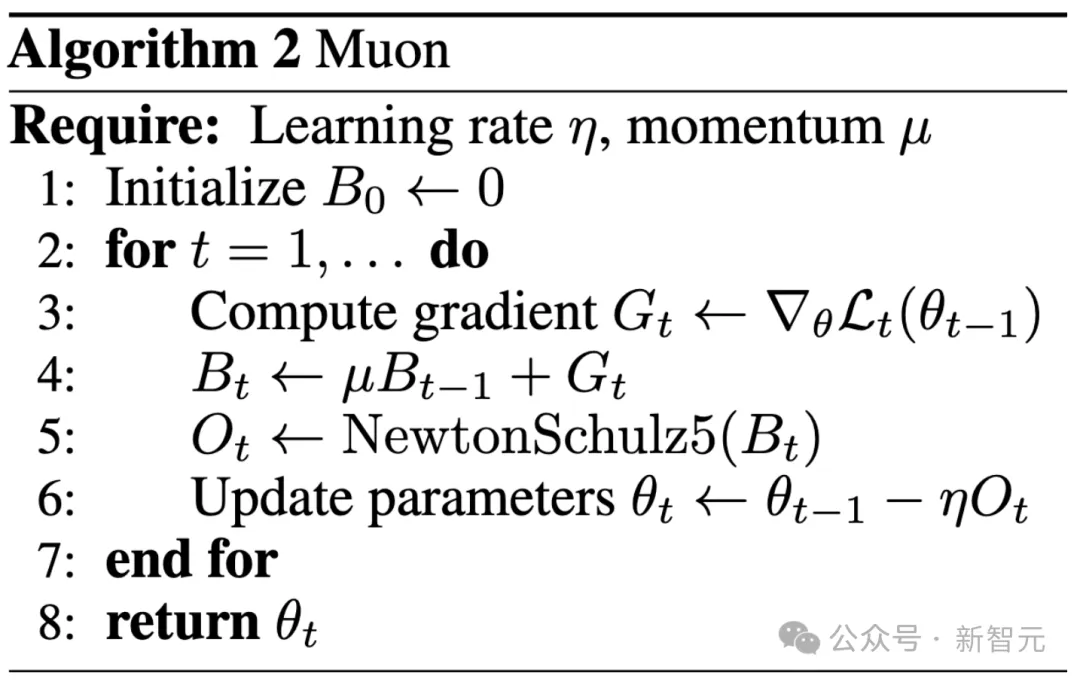

为了实现高吞吐量,TPU在硬件层面采用了“脉动阵列”(Systolic Array)架构。该架构由大量简单的处理单元(PE)构成网格。数据流从阵列的边缘输入,在每个时钟周期同步地、一步步地流经相邻的处理单元。每个单元执行一次乘法累加运算,并将中间结果直接传递给下一个。

这种设计使得数据在阵列内部被高度复用,最大限度地减少了对高延迟、高功耗主内存的访问,从而实现了惊人的处理速度。

而其卓越能效的秘诀,则在于软硬件协同的“提前编译”(Ahead-of-Time Compilation)策略。传统的通用芯片需要高能耗的缓存来应对多样的、不可预测的数据访问。TPU则不同,它的编译器在程序运行前就完整规划好了所有数据路径,这种确定性使其无需复杂的缓存机制,从而大幅降低了能耗。

在TPU的设计上,谷歌主导整体架构与功能定义,博通Broadcom参与了部分芯片的中后端设计工作,目前,Google TPU主要由台积电代工生产。

随着大语言模型参数的急剧扩张,AI计算任务正在从“训练”走向“推理”。这时,作为通用算力单元的GPU,开始显露出成本以及功耗过高的问题。

而TPU从设计之初就专门瞄准了AI计算,具有很高的性价比优势。据报道,谷歌TPU算力成本仅为OpenAI使用GPU成本的1/5,性能功耗比更是优于同代GPU。

因此,为了抓住市场,谷歌围绕着自己的TPU架构,打造了一系列产品与生态。

谷歌造芯这十年

谷歌第一代TPU (v1) 于2015年推出,通过高度简化的专用设计,实现了超越同期CPU与GPU的能效比,并在AlphaGo等项目中展示了其高效能,从而验证了AI ASIC的技术路径。

随着研发深入,训练环节的算力瓶颈日益凸显,促使TPU的设计方向转向系统级解决方案。2017年发布的TPU v2为此引入了BF16数据格式以支持模型训练,并配置了高带宽内存(HBM)。

更为关键的是,v2通过定制的高速网络将256个芯片单元互联,首次构建了TPU Pod系统。随后的TPU v3通过增加计算单元数量和引入大规模液冷技术,实现了性能的显著提升。

TPU v4的发布带来了互联技术的重大革新,其核心是采用了光学电路交换(OCS)技术,实现了TPU Pod内部网络拓扑的动态重构,从而提升了大规模训练任务的容错能力与执行效率。进入v5与v6 (Trillium) 阶段,TPU产品线呈现出分化策略,形成了分别侧重于极致性能的'p'系列与能效比的'e'系列,以适应多样化的AI应用场景。

2025年Google TPU的全年出货量预计为250万片。v5系列总出货量预计为190万⽚,其中v5e占⽐约120万⽚,v5p占⽐约70万⽚, v6系列预计总出货量为60万⽚,⽬前仅v6e在市场上销售,⽽v6p将在第四季度上市,约10-20万⽚左右。预计到2026年,总体TPU销量将超过300万片。

在今年的谷歌云大会上,谷歌发布了第七代TPU,代号“Ironwood”。

Ironwood是谷歌迄今为止性能最强、能效最高且最节能的TPU芯片,其峰值算力达到4614 TFLOPs,内存容量为192GB,带宽高达7.2 Tbps,每瓦峰值算力为29.3 TFLOPs。此外,Ironwood首次支持FP8计算格式,并在张量核和矩阵数学单元中实现这一功能,这使得其在处理大规模推理任务时更加高效。

Ironwood最高配集群可拥有9216个液冷芯片,峰值算力可达42.5 ExaFLOPS,是世界上最大的超级计算机El Capitan的24倍以上。其支持大规模并行处理和高效内存访问,适用于复杂的推理任务如大型语言模型和混合专家模型。

事实上,Ironwood的整体性能已经十分接近英伟达B200,甚至在一些方面还有所超越。

当然,英伟达的统治力不仅在于其硬件性能,更在于整个CUDA生态。谷歌深知这一点,因此,它也构建了JAX这样的,能在TPU上运行的高性能计算Python库。

谷歌还发布了其模型流水线解决方案“Pathway”,用于向外部开发者训练大型语言模型(LLM)。将其作为训练模型的必备手册,研究人员无需重新设计模型即可开发Gemini等LLM。

有了上述的一整个“军火库“,谷歌终于可以和英伟达掰掰手腕了。

谷歌vs英伟达

投资银行D.A. Davidson分析师Gil Luria在最新报告中指出,过去一年以来谷歌母公司Alphabet大幅缩小与英伟达的差距,如今已成为“最好的英伟达替代方案”。

报告显示,过去半年,围绕Google Cloud TPU的开发者活跃度激增了约96%。

Gil Luria与前沿AI实验室的研究人员和工程师交流后发现,业内普遍看好谷歌TPU。因此Luria认为,若谷歌将TPU业务与DeepMind部门合并并将它们分拆上市,估值或将高达9000亿美元。

AI独角兽Anthropic此前使用亚马逊的Trainium芯片来训练模型,最近,该公司被发现正在招聘TPU内核工程师;马斯克旗下的人工智能公司xAI也对采购TPU表现出兴趣。这一切都说明了业界对于TPU的认可。

而谷歌自身也在积极行动。首先,谷歌有意在公司内部进行从英伟达GPU到自研TPU的迭代。Omdia数据显示,2024年估计谷歌订购16.9万台Hopper 架构GPU,在五大云厂商中排名最后,约为微软的三分之一。同时,谷歌内部已部署了约150万颗TPU。

谷歌的对外战略,就是文章开头提到的,对那些使用英伟达芯片的数据中心供应TPU。据报道,为了与Floydstack达成合作,谷歌将提供最高32亿美元的备选担保支持,若Fluidstack无力支付纽约新数据中心的租赁费用,谷歌将补足差额。

根据野村证券最新报告,预计到2026年,ASIC总出货量很可能会第一次超过GPU。而TPU正是目前最成熟的ASIC。

英伟达需要紧张起来了。

结语

市场对谷歌TPU的积极接受,反映出越来越多的公司想摆脱英伟达“一卡难求“的困境,寻求更高的性价比和更多元、稳定的供应链。

而借此机会挑战英伟达的,也不只有谷歌一家公司。供应链数据显示,meta将于2025年第四季度推出其首款ASIC芯片MTIA T-V1。它由博通设计,具有复杂的主板架构,并采用液冷和风冷混合技术。

到2026年年中,MTIA T-V1.5将进行进一步升级,芯片面积将翻倍,超过英伟达下一代GPU Rubin的规格,其计算密度将直接接近英伟达的 GB200 系统。2027年的MTIA T-V2可能会带来更大规模的CoWoS封装和高功率机架设计。

报告指出,根据供应链估计,meta的目标是到2025年底至2026年实现100万至150万件ASIC出货量。

微软、亚马逊同样有自研的ASIC芯片,正在对这片被GPU霸占的市场虎视眈眈。

对此,英伟达也有自己的反击手段。今年5月,英伟达正式发布NVlink Fusion。NVlink Fusion允许数据中心将英伟达GPU与第三方CPU或定制化AI加速器混合使用,标志着英伟达正式打破硬件生态壁垒。

近日,英伟达执行副总裁暨首席财务官Colette Kress在高盛组织的会议上谈及了对于AISC芯片所带来的竞争看法,称英伟达GPU更具性价比。

一场大戏已经拉开了帷幕。无论是万亿美元的市场规模,还是未来AI时代硬件结构的定义权,都值得几大巨头为之疯狂。

这一战,谁都有不能输的理由。

京公网安备 11011402013531号

京公网安备 11011402013531号